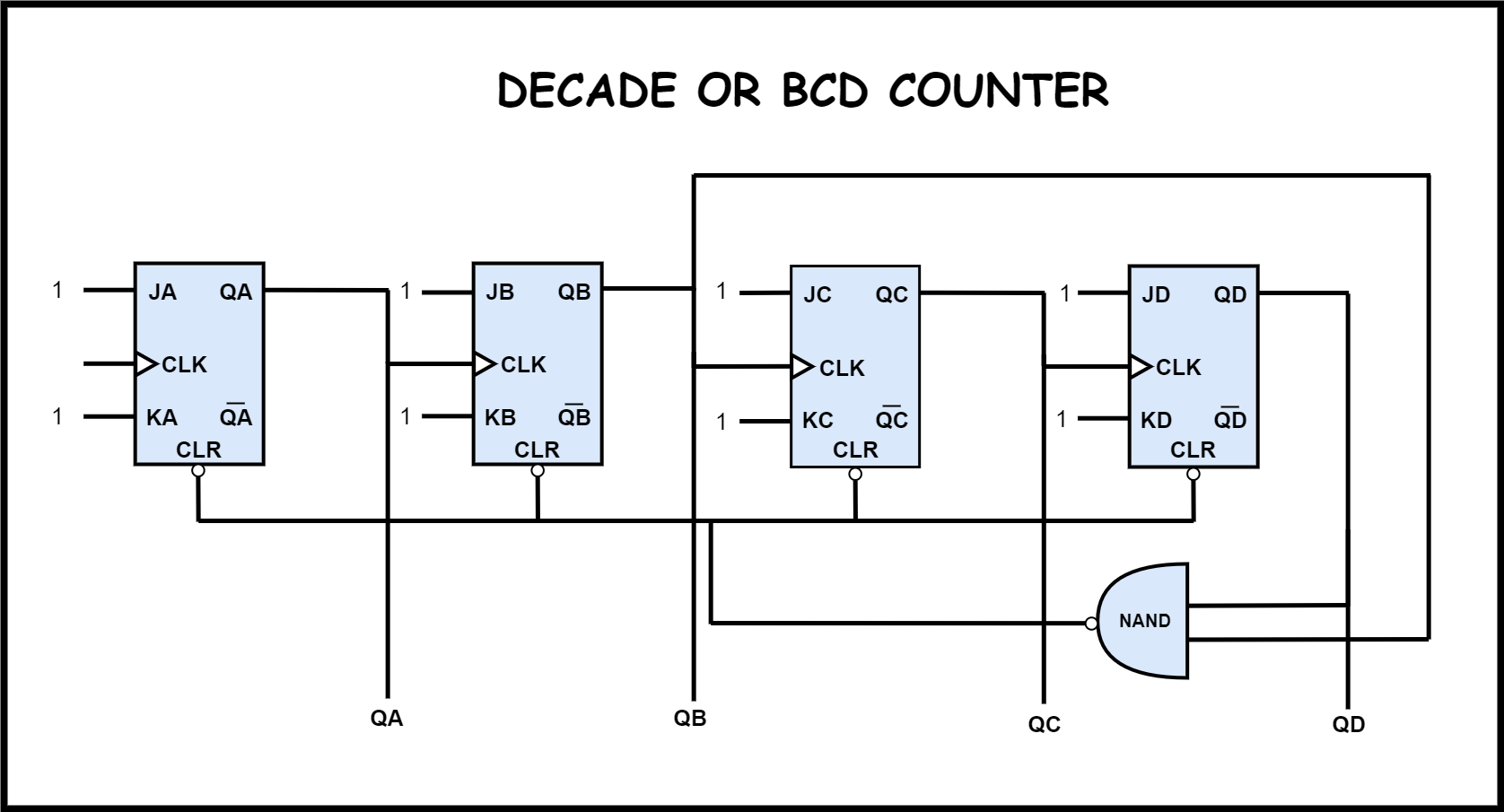

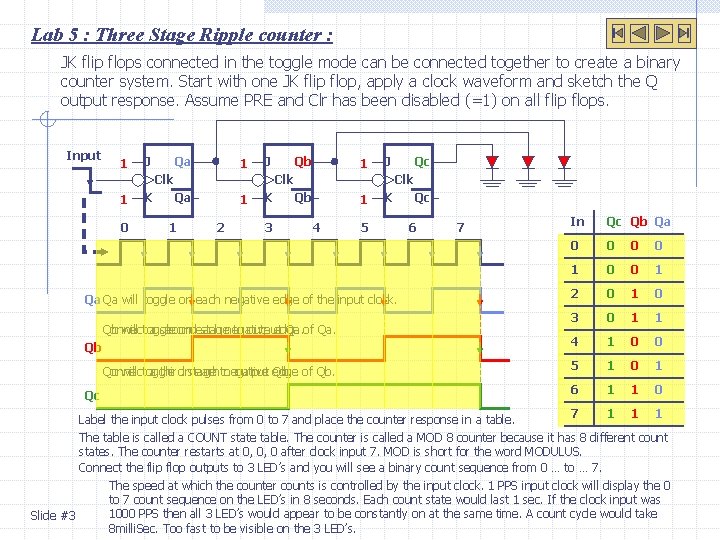

Solved] Design an asynchronous MOD-13 ripple counter using negative edge clocked J-K flip flops. The flip flops have an asynchronous, low-true clear... | Course Hero

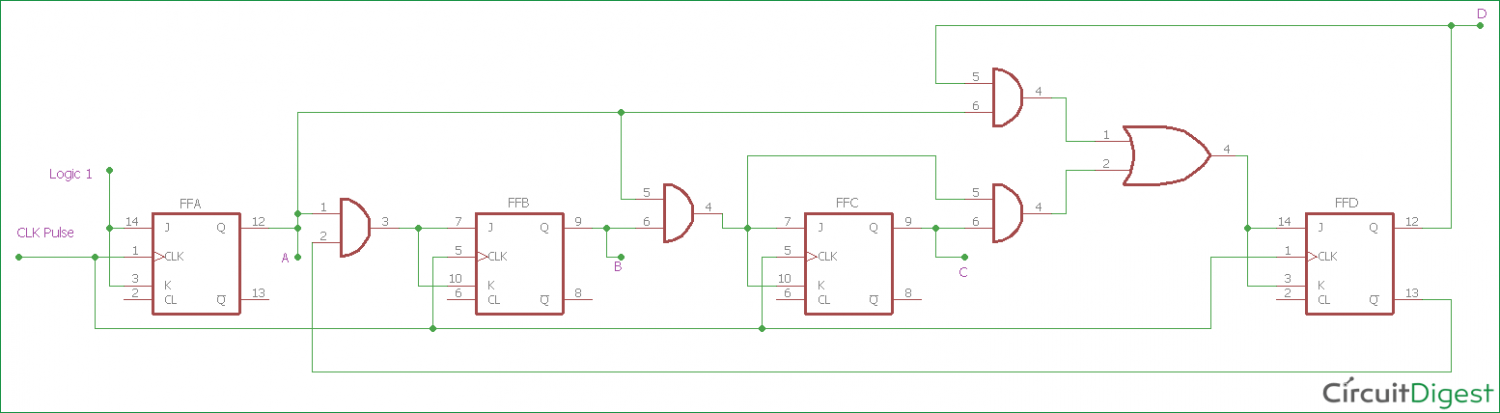

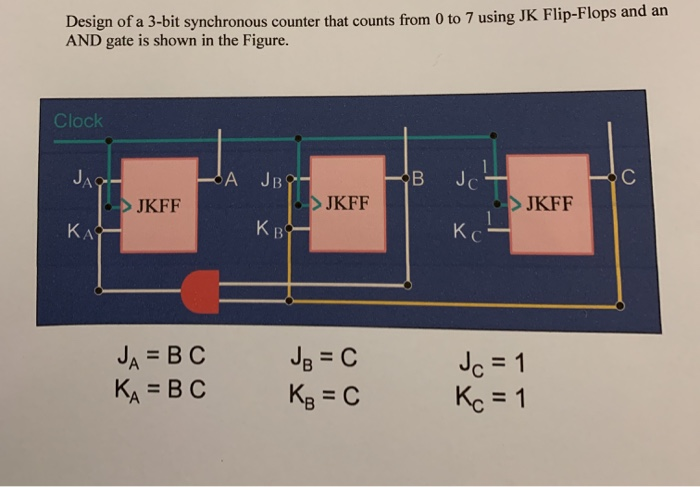

How to design a synchronous counter using D-type flip-flops for getting the following sequence, 0-3-6-9-12-15-0 - Quora